|

Multicore research with Beehive |

|

Multicore research with Beehive |

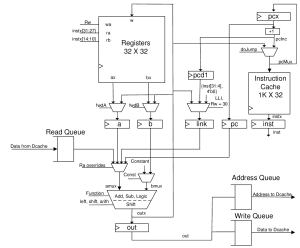

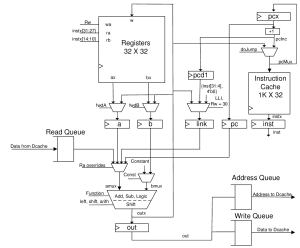

The goal of this IAP class is to get familiar enough with low-level system software and Verilog to start doing research on the hardware/software interface for multicore processors. MSR Silicon Valley has developed a new multi-core processor, implemented by configuring an FPGA. On an entry-level Xilinx FPGA, it has 13 100 MHz RISC processors, which occupy about half of the FPGA. This includes the memory system and the Ethernet controller, but not cache coherence. Beehive comes with an open-source C toolchain to develop software, and using the Xilinx tools one can modify the hardware/software interface. Tentatively, students will develop a simple distributed shared-memory system, and accelerate its performance by making Verilog modifications, but students with their own proposals for projects are welcome. The intended audience is both graduate and undergraduate students who want to do research in design of hardware/software interface of multicore systems. We will provide FPGA boards for use during the course.

Length: 6 days, Jan 12-15, 18-19, 2010.

Time: 11am-2pm

Location: 8th floor reading room

$ git clone http://pdos.csail.mit.edu/beehive-class.git

...Microsoft Research Silicon Valley for supplying the source code for the Beehive hardware and software toolchain, and Xilinx for donating the XUP5 boards: