## Apiary: Software Tools for Beehive v2

Thomas L. Rodeheffer Microsoft Research, Silicon Valley

December 16, 2009

# Contents

| 1 | Introduction |                                   |    |  |  |  |  |  |  |

|---|--------------|-----------------------------------|----|--|--|--|--|--|--|

|   | 1.1          | Tools                             | 1  |  |  |  |  |  |  |

|   | 1.2          | File types                        | 2  |  |  |  |  |  |  |

|   | 1.3          | Getting the tools                 | 3  |  |  |  |  |  |  |

| 2 | C Co         | ompiler - Bgcc1                   | 4  |  |  |  |  |  |  |

|   | 2.1          | Making a bootable image           | 4  |  |  |  |  |  |  |

|   |              | 2.1.1 Compiling C to assembler    | 4  |  |  |  |  |  |  |

|   |              | 2.1.2 Assembling                  | 5  |  |  |  |  |  |  |

|   |              | 2.1.3 Loading                     | 6  |  |  |  |  |  |  |

|   |              | 2.1.4 Making a bootable image     | 7  |  |  |  |  |  |  |

|   | 2.2          | Startup code                      | 7  |  |  |  |  |  |  |

| 3 | Asse         | embler - Bas                      |    |  |  |  |  |  |  |

|   | 3.1          | Running Bas                       | 8  |  |  |  |  |  |  |

|   | 3.2          | Source format                     | 9  |  |  |  |  |  |  |

|   | 3.3          | Comments                          | 9  |  |  |  |  |  |  |

|   | 3.4          | Identifiers, numbers, and strings | 9  |  |  |  |  |  |  |

|   | 3.5          | <b>e</b>                          | 10 |  |  |  |  |  |  |

|   | 3.6          |                                   | 11 |  |  |  |  |  |  |

|   | 3.7          |                                   | 11 |  |  |  |  |  |  |

|   | 3.8          |                                   | 12 |  |  |  |  |  |  |

|   | 3.9          |                                   | 12 |  |  |  |  |  |  |

|   | 3.10         |                                   | 12 |  |  |  |  |  |  |

|   |              |                                   | 12 |  |  |  |  |  |  |

|   |              |                                   | 13 |  |  |  |  |  |  |

|   |              |                                   | 13 |  |  |  |  |  |  |

|   |              |                                   | 14 |  |  |  |  |  |  |

|   |              |                                   | 14 |  |  |  |  |  |  |

|   |              |                                   | 15 |  |  |  |  |  |  |

|   |              |                                   | 16 |  |  |  |  |  |  |

|   |              |                                   | 17 |  |  |  |  |  |  |

|   |              |                                   | 17 |  |  |  |  |  |  |

|   |              |                                   | 17 |  |  |  |  |  |  |

|   |              |                                   |    |  |  |  |  |  |  |

|   |       | 3.10.11 Simulator control                  |

|---|-------|--------------------------------------------|

|   | 3.11  | Directives                                 |

|   |       | 3.11.1 Segment selection directives        |

|   |       | 3.11.2 Advance current location directives |

|   |       | 3.11.3 Align current location directives   |

|   |       | 3.11.4 Emit words or bytes directives      |

|   |       | 3.11.5 Emit string directives              |

|   |       | 3.11.6 Region nesting directives           |

|   |       | 3.11.7 Assume register directives          |

|   |       | 3.11.8 Global symbol directive             |

|   |       | 3.11.9 Local symbol directive              |

|   |       | 3.11.10 Common request directive           |

|   |       | 3.11.11 Include directive                  |

|   |       | 3.11.12 Commentary directives              |

|   | 3.12  | Predefined symbols                         |

|   |       |                                            |

| 4 | Utili |                                            |

|   | 4.1   | Archiver - Bar                             |

|   | 4.2   | Loader - Bld                               |

|   | 4.3   | Image maker - Bimg                         |

|   | 4.4   | Virtex mem file maker - Bvmem 28           |

|   | 4.5   | File of bytes processor - Bfiledata    28  |

| 5 | Simi  | ılator - Bsim 30                           |

| 5 | 5.1   | Running Bsim   30                          |

|   | 5.2   | Cache preload requests                     |

|   | 5.3   | Physical memory                            |

|   | 5.4   | Simulated coprocessors                     |

|   | 5.5   | Simulator controls                         |

|   | 5.6   | Interactive debugger                       |

|   | 5.0   |                                            |

| Α | Beeh  | ive architecture 34                        |

|   | A.1   | ALU function                               |

|   |       | A.1.1 ALU argument A                       |

|   |       | A.1.2 ALU argument B                       |

|   | A.2   | Major Operation                            |

|   | A.3   | Condition codes                            |

|   | A.4   | Reserved                                   |

|   | A.5   |                                            |

|   |       | A.5.1 Debug unit                           |

|   | A.6   |                                            |

|   |       | A.6.1 Address queue value                  |

|   |       | A.6.2 ASLI interface                       |

|   |       | A.6.3 Data cache controller                |

|   |       | A.6.4 Inter-core message controller        |

|   |       | A.6.5 Lock controller                      |

|   | A.7         | Instruction fetch                   |

|---|-------------|-------------------------------------|

| В | Obje        | ect file format                     |

|   | <b>B</b> .1 | Archive element                     |

|   | B.2         | Object element                      |

|   | B.3         | Segment element                     |

|   | B.4         | Word element                        |

|   | B.5         | Zero element                        |

|   | B.6         | Patch element                       |

|   | B.7         | Expression patch element            |

|   | B.8         | Extrn element                       |

|   | B.9         | Globl element                       |

|   | B.10        | Local element                       |

|   | B.11        | Comm element                        |

| ~ | <b>G A</b>  |                                     |

| С |             | ware conventions                    |

|   | C.1         | Register usage                      |

|   | C.2         | Memory layout                       |

|   | C.3         | C subroutine linkage                |

|   |             | C.3.1 Return value                  |

|   |             | C.3.2 Layout of the parameter block |

|   |             | C.3.3 Integral number of words      |

|   |             | C.3.4 Passing the parameter block   |

|   |             | C.3.5 Calling the subroutine        |

|   |             | C.3.6 Subroutine entry              |

|   |             | C.3.7 Subroutine return             |

|   | C.4         | Instruction schemas                 |

|   |             | C.4.1 Fetching from memory          |

|   |             | C.4.2 Storing into memory           |

|   |             | C.4.3 General schema                |

## **Chapter 1**

# Introduction

The Beehive software tools are a collection of programs to assist in software development for Beehive. Available tools include a C compiler, relocating assembler, loader, image maker, and simulator.

## 1.1 Tools

The available software tools are described briefly as follows:

- Bgcc1 The Beehive C compiler. This is a port of the GNU C compiler version 4.3.3. Chapter 2 describes how to use the C compiler.

- Bas The Beehive relocating assembler. Chapter 3 describes the assembler in detail.

- Bar The Beehive archiver, which gathers a collection of relocatable object files into a library archive. Section 4.1 describes how to use the archiver.

- Bld The Beehive loader, which loads a collection of relocatable object files into an executable object file, binding external references. Section 4.2 describes how to use the loader.

- Bimg The Beehive image maker, which constructs a binary memory image of an executable object file. Section 4.3 describes how to use the image maker.

- Bvmem The Beehive Virtex mem file maker, which constructs code and data Virtex mem files from an executable object file. Section 4.4 describes how to use the Virtex mem file maker.

- Bsim The Beehive simulator, which simulates the execution of an executable object file. Chapter 5 describes how to use the simulator.

- Bsiming A version of the Beehive simulator that takes its input from a binary memory image.

Bfiledata A utility that converts a file of bytes into a C source file that initializes a global to an array of those bytes. Section 4.5 describe how to use the file data utility.

## **1.2** File types

The various file types on which the tools operate are distinguished by convention using standard extensions. The standard extensions and file types are as follows:

- .c A source file written in C.

- .h A header (include) file for a C program.

- .as A source file written in assembly language.

- . s An intermediate assembler source file produced by compiling a C source file.

- . A relocatable object file produced by assembling an assembler source file. For convenience in tool development, a relocatable object file is an XML text file. The format of this file is described in Appendix B.

- .a An archive of relocatable object files produced by the archiver. An archive file is treated as a library by the loader, which loads as many relocatable object files from it as are needed to satisfy unbound external references. For convenience in tool development, an archive file is an XML text file. The format of this file is described in Appendix B.

- . out An executable object file. An executable object file is produced by the loader from a collection of relocatable object files and archives. Technically, an executable object file is identical in format to a relocatable object file. However, the expectation is that the executable object file will have no unbound external references. The start address is the value of the symbol "main".

- . img An executable image file. An executable image file is produced by the image maker from an executable object file and it consists of a binary memory image starting at some specified word index in memory. The program is expected to start execution at the first word in the image.

- .mem A Virtex mem file. A Virtex mem file is produced by the Virtex mem file maker from an executable object file. The program is expected to start execution at code address 0.

- .lst A listing file. The assembler produces a listing file as one of its outputs during assembly. The listing file is in text format and is meant for human consumption.

- .map A map file. The loader produces a map file as one of its outputs during assembly. The map file is in text format and is meant for human consumption.

The following chapters describe these tools and file types in detail.

## **1.3** Getting the tools

The Beehive software tools can be obtained from

```

\\msr-svc\files\users\tomr\Beehive\apiary-distv2.tar

```

Make a directory that you will use as the root directory for Beehive software tools. There is no required name for the directory but henceforth we will call it APIARY. It would be a good idea to define an environment variable APIARY that contains the name of the root directory. (In the future this may become mandatory.)

Unzipping the Beehive software tools file into APIARY reveals the following directory structure:

APIARY/bin Tool executables and dlls.

APIARY/include Include files.

APIARY/lib Library files.

APIARY/src/lib Source files used to build the library files.

APIARY/src/hello Source files of a simple C program.

In order to execute the Beehive software tools, you have to add APIARY/bin to your PATH environment variable.

## **Chapter 2**

# C Compiler - Bgcc1

Bgcc1 is a port of the GCC compiler version 4.3.3 to the Beehive. Appendix C describes the software conventions used by Bgcc1 in its employment of the Beehive architecture.

## 2.1 Making a bootable image

Converting a C program into a bootable image file takes four steps.

- 1. Compiling the C source code to assembler.

- 2. Assembling the assembler source code to a relocatable object file.

- 3. Loading the relocatable object file with startup code and libraries to produce an executable object file.

- 4. Converting the executable object file to a bootable image file.

Starting with a C source file *source.c*, the recommended commands for performing these four steps are as follows, where *APIARY* stands for the name of the Apiary root directory:

Bgcc1 -quiet -std=c99 -fno-builtin -O2 -IAPIARY/include source.c Bas -x -datarota=2 source.s Bld -o source.out -codebase=1000 -datafloat APIARY/lib/base.o source.o -LAPIARY/lib -lc -lgcc Bimg source.out

Next these steps are described in more detail.

#### 2.1.1 Compiling C to assembler

Bgcc1 compiles a C source file to assembler code. Bgcc1 is invoked using the command line

Bgcc1 [options] source.c

One source file is expected. The C source code *source.c* is compiled to the assembler source file *source.s* using the same base file name but replacing the .c extension with .s

Options start with a hypen (-). GCC supports a hideously enormous number of options. For a listing, use the command

Bgcc1 --help

or refer to GCC documentation such as http://gcc.gnu.org/onlinedocs/ gcc/. Note that some of the documented options pertain to the so-called gcc driver and not to the compiler proper, which is what Bgcc1 is.

The recommended command line to compile an example C source file *source.c* to the assembler file *source.s* is as follows:

Bgcc1 -quiet -std=c99 -fno-builtin -O2 -IAPIARY/include source.c

The arguments are interpreted as follows:

- -quiet Cause the compiler not to print lots of generally uninteresting compilation statistics.

- -std=c99 Declare that we want the c99 standard dialect of C. Without this, you get an older dialect that prohibits declaring variables other than at the start of blocks, which is painful.

- -fno-builtin Tell the compiler not to think it understands what printf and friends do.

- -O2 Ask for optimization level 2. At this level, you get nice data flow analysis and register allocation.

- -IAPIARY/include Add the standard Apiary include directory to the search path. *API-ARY* is the Apiary root installation directory (see Section 1.3), preferably stored in the APIARY environment variable.

source.c This is the C source file.

#### 2.1.2 Assembling

The assembly source code produced by Bgcc1 has several properties that affect how it must be assembled. (1) Bgcc1 uses symbol names for external references without ever defining them. (2) Bgcc1 assumes that the data segment is byte-addressed.

The recommended command line to assemble the compiler-generated assembler source file *source.s* to the relocatable object file *source.o* is as follows:

Bas -x -datarota=2 source.s

The arguments are interpreted as follows:

-x Cause the assembler to treat each undefined symbol as an external reference.

-datarota=2 Specify that the data segment is byte-addressed.

source.s This is the assembler source file.

#### 2.1.3 Loading

Converting the relocatable object file into an executable object file requires supplying startup code and various libraries. The startup code prepares the C environment and is described in Section 2.2.

The library *libc.a* is a basic C library containing malloc, some string routines, and simple input and output including printf. It also includes some beehive-specific support routines described in Appendix **??**.

The library *libgcc.a* contains compiler runtime support routines for arithmetic, shifting, and for fetching and storing bytes and shorts. This library must always appear last.

Assuming that the intent is eventually to produce a binary memory image that can be loaded by the level 1 Beehive boot loader, the requirements of this boot loader must also be kept in view. These requirements are as follows. (1) The binary memory image must be a continuous sequence of words starting at memory word index 0x1000. (2) The program must start execution at memory word index 0x1000. These requirements can be satisfied by supplying the proper arguments to Bld.

The recommended command line to load the compiler-generated and assembled relocatable object file *source.o* to produce the executable object file *source.out* is as follows:

```

Bld -o source.out -codebase=1000 -datafloat APIARY/lib/base.o source.o -LAPIARY/lib -lc -lgcc

```

The arguments are interpreted as follows:

- -o source.out Specify that the output file is source.out

- -codebase=1000 Specify that the code segment will be relocated to start at memory word index 0x1000. This is the required base load address for the level 1 Beehive boot loader.

- -datafloat Specify that the data segment will be relocated to start after the end of the code segment.

- APIARY/lib/base.o Cause the loader to start off by loading the startup code which is found in the library module base.o. APIARY is the Apiary root installation directory (see Section 1.3), preferably stored in the APIARY environment variable.

- **source.o** Cause the loader to continue by loading the relocatable object code compiled and assembled from source.c. Additional relocatable object files may be listed at this point.

- -LAPIARY/lib Cause the loader to add the directory APIARY/lib to the library search path.

- -lc Cause the loader to find the library archive libc.a on the library search path and load all relocatable object files needed to satisfy external references.

- -lgcc Cause the loader to find the library archive libgcc.a on the library search path and load all relocatable object files needed to satisfy external references.

#### 2.1.4 Making a bootable image

Assuming that the executable object file was loaded with the proper arrangement to become a bootable image file, the actual bootable image file is produced by Bimg. The recommended command line is as follows:

Bimg source.out

The arguments are interpreted as follows:

source.out This is the executable object file.

The resulting bootable image file is source.img

## 2.2 Startup code

The startup code prepares the C execution environment. It contains the executable entry point main and has the responsibilities of (1) initializing the assume zero register zero, (2) initializing the stack pointer register sp, and then (3) calling the C language main subroutine main with no parameters. Software register usage is described in Section C.1.

Since many arrangements for booting programs require that the program start execution at the first word loaded, it is also convenient for the startup code to be loaded first so that the executable entry point main occurs in the correct place. Such an arrangement permits the C language main subroutine to appear anywhere in memory, Note that C language global symbol names are prefixed with an underscore (\_) in assembly code. Thus the C language main subroutine can be distinguished from the executable start address.

The recommended startup code module base.o sets up a small stack which should suffice for simple programs. However, an alternate startup module may be provided. The Apiary library includes the following startup code object files:

APIARY/lib/base.o Includes a 200 word stack in the data segment.

- APIARY/lib/basehs.o Initializes the stack pointer to 0xffffffc, which is the highest word address in data memory.

- APIARY/lib/basemc.o Multicore startup code. Includes an array of 16 stacks in the data segment, each 256 words long and aligned on a cache line boundary. Initializes the stack pointer to the top of the stack corresponding to the current core. Note that since global variables are in general not aligned on cache line boundaries they are problematic to use in multicore programming, since flushing one variable may overwrite others with stale data.

## **Chapter 3**

# **Assembler - Bas**

Bas is a relocating assembler for Beehive [1] version 2. The instruction set is summarized in Appendix A. Bas reads one or more assembler source files and writes a relocatable object file and, if requested, a listing file. The format of the object file is described in Appendix B.

## 3.1 Running Bas

Bas is invoked using the command line

Bas [options] sourcea.s sourceb.s ...

- Options start with a hypen (-). The following options are supported:

- -o out Use out as the file name for the relocatable output file. Note there is a space between -o and out. The default is to use name of the first input file with its extension replaced with .o

- -lst *lst* Use *lst* as the file name for the listing file. Note there is a space between -lst and *lst*. The default is to omit the listing file.

- -x Automatically define all otherwise undefined symbols as external references to global symbols.

- -Idir Add the directory *dir* to the list of directories searched for include files. Note there is no space between -I and *dir*.

- -codebase=n Set the base of the default code segment .text to word index n, where n is a hexadecimal number. The default is 0. Note that this is a word index, so it is unaffected by address rotation. The loader typically changes the base during relocation, so the base given to Bas really only has significance for the listing file.

- -database=n Set the base of the default data segment .data to word index n, where n is a hexadecimal number. The default is 0. Note that this is a word index, so it

is unaffected by address rotation. The loader typically changes the base during relocation, so the base given to Bas really only has significance for the listing file.

- -coderota=n Set the rotation of code addresses to n, where n is a hexadecimal number. The default is 0, which produces a word-addressed architecture for code addresses. The code address rotation controls how current location advances in all code segments.

- -datarota=n Set the rotation of data segment addresses to n, where n is a hexadecimal number. The default is 0, which produces a word-addressed architecture for data addresses. The data address rotation controls how the current location advances in all data segments and in the absolute segment.

Although any extension may be used for the assembler source files, the extension .as is recommended for user-written source files. Multiple source files are concatenated to form a single input source program. The following extensions are recommended for the output files:

.lst the listing file .o the object file

## **3.2** Source format

The assembler source files consist of comments, label definitions, symbol definitions, instructions, and directives. Generally each source line contains zero or more label definitions and, optionally, an equate definition or an assembler statement. However, multiple logical lines can be placed on the same physical line by separating them with semicolons.

## 3.3 Comments

An end-of-line comment starts with // and goes up to the end of the line. A multiline comment starts with / \* and ends with a matching \*/ and may be nested. Comments are treated as white space.

```

// this is an end-of-line comment

/* this is a multiline comment

/* which may be nested */ */

```

### **3.4** Identifiers, numbers, and strings

A word is a non-empty sequence of alphabetic characters, digits, ".", and "\_". An identifier is a word that does not start with a digit. An identifier that starts with "." is special as explained later. A number is a word that starts with a digit. As in C, if the number starts with "0x" it is interpreted in hexadecimal, otherwise if it starts with "0" it is interpreted in octal, otherwise it is interpreted in decimal.

- + positive

- negative

- ~ bit complement

- \$ register number

#### Table 3.1: Prefix operators

- + addition

- subtraction

- bit or

- & bit and

- ^ bit xor

- \* multiplication

- / unsigned division

- % unsigned remainder

- ROR rotate right

- ROL rotate left

- LSR logical shift right

- ${\tt LSL} \ logical \ shift \ left$

- ASR arithmetic shift right

- ASL arithmetic shift left (same as LSL)

Table 3.2: Infix operators

A string is enclosed in double quotes (") and has the usual escapes using backslash ( $\backslash$ ) as in C. A string can span multiple lines. Escaping the newline prevents the newline from being part of the string. A string of up to four characters can be used as a constant in an expression. The first character defines the low order eight bits, the second character (if any) the next eight bits, and so on, with any leftover bits being defined as zero.

## 3.5 Expressions

Words can be combined into expressions using parenthesis, prefix operators, and infix operators. Prefix operators have precedence over infix operators. For simplicity, all infix operators have the same precedence and associate to the left. Table 3.1 shows the prefix operators and Table 3.2 the infix operators. Note that the infix operators ROR, ROL, and so on are reserved words in the grammar. Although the infix operator ASL is provided for completeness, it is the same as LSL.

As explained in Section 3.7, expressions compute values and values have types. In most cases the arguments of operators must be absolute numbers.

### 3.6 Registers

Ordinary registers are specified via register numbers using the dollar sign (\$) prefix operator. The ordinary registers are 0, 1, 2, etc. You can also write expressions such as (3+4) but this is probably not very useful. An identifier may be defined as an ordinary register.

Special registers are specified via the following predefined identifiers:

pc the program counter register, read via Ra overload 31link the link register, read via Ra overload 30rq the read queue register, read via Ra overload 29wq the write queue register, written via Rw overload 31

Bas ensures that ordinary registers and special registers are used only in their proper places. For example, Bas checks that \$31 is not specified for Ra, which would not work because of Ra overloading.

## **3.7** Values and types

Expressions compute values and values have types.

The simplest type is an *absolute number* such as 0, 1, 2, etc. Strings that are used as constants in an expression are also considered to be absolute numbers. Absolute numbers can be combined in an expression using any of the arithmetic and bit operators.

Another type is a *register number*. A register number is obtained by applying the prefix register number operator (\$) to an absolute number. Each of the special registers is also its own type. Register numbers and special registers cannot be further combined in an expression.

A *relocatable offset* is another class of types. Examples of these types are offsets in a segment and offsets from an external reference to a global symbol. Each different basis of relocation gives rise to a unique type. So, for example, offsets in one code segment are one type, offsets in another code segment are a second type, offsets in a data segment are a third type, and offsets from a particular external symbol are yet a fourth type. Two relocatable offsets can be subtracted from one another, producing an absolute number, provided that the offsets are of the same type. An absolute number can be added or subtracted from a relocatable offset with the obvious result.

The final type is the *exprpatch*. An exprpatch is a symbolic expression tree in which the leaves are absolute numbers and relocatable offsets and the operators are addition, subtraction, bitwise inclusive or, bitwise clear, and rotation. The exprpatch is the general type that is handled by the relocating loader. Observe that absolute numbers and relocatable offsets can be promoted trivially into exprpatches.

Bas constructs an exprpatch as its internal representation of how to convey information from "long\_ld" and similar instructions to the loader. Another operator available in the exprpatch is "mbz", which is a loader-checked assertion that certain bits in a symbolic value must be zero. Bas uses the mbz operation to convey information from the "x\_lli" instruction to the loader. Unfortunately, Bas currently does not permit the user to construct an exprpatch as the result of an expression. This deficiency will be fixed when time permits.

## **3.8 Label definitions**

A label definition consists of an identifier followed by a colon:

```

identifier: // a label definition

```

The identifier is assigned the address of the current location. Note that the current location can be a relocatable offset in a segment or an absolute value.

Multiple label definitions may appear at the start of a line. Any given identifier can be defined at most once.

## **3.9** Equate definitions

An equate definition consists of an identifier followed by an equals sign (=) followed by an expression followed by the end of the line. Any identifiers used in the expression must be defined earlier in the input source.

identifier = expression // an equate definition

The identifier is assigned the value of the expression. Note that values come in various types. A value can be an absolute number, a relocatable offset, a register number, or one of the special registers.

## 3.10 Instructions

An instruction consists of an opcode followed by a comma-separated list of arguments:

```

opcode arg,arg,arg,...

```

Each argument is an expression. The opcode defines a semantic operation with a given number of arguments that is to be assembled into a certain number of machine instructions. Most opcodes assemble into one instruction but a few assemble into two instructions. The assembled instructions are emitted into the current segment.

Although lexically an opcode is an identifier, it is not in the same namespace as predefined and user defined identifiers. Opcodes are not reserved words. The various classes of instructions are described next.

#### **3.10.1** Basic functions

The Beehive CPU supports eight basic arithmetic and logical functions which are specified via opcodes as follows:

```

add w,a,b // w = a + b

sub w,a,b // w = a - b

or w,a,b // w = a | b

orn w,a,b // w = a | ^{b}

and w,a,b // w = a \& b

and w,a,b // w = a \& ^{b}

xor w,a,b // w = a ^{b}

```

Each of the arguments is an expression that specifies a value as follows:

w a register number or a special register wq or link.

a a register number or a special register pc, link, or rq.

**b** a register number or an absolute number 0..0xfff.

The instruction assembles into a machine instruction using the NOSHIFT op in order to permit the widest range of constants.

#### **3.10.2** Basic function with address queue pushes

The Beehive CPU has machine instructions that push the result of any of the eight basic functions onto the address queue in addition to writing it to the destination register. These machine instructions are specified by opcode families derived from each of the basic function opcodes. For simplicity, we show only the opcode family for "add". Analogous families exist for each of the other basic functions.

aqr\_add w,a,b // aqr = w = a + b (memory read) aqw\_add w,a,b // aqw = w = a + b (memory write)

Each of the arguments is an expression that specifies a value as follows:

w a register number or a special register wq or link.

a a register number or a special register pc, link, or rq.

b a register number or an absolute number 0..0xfff.

#### **3.10.3** Basic function with shifts

The Beehive CPU has machine instructions that apply an arbitrary shift of any of five types to the result of any of the eight basic functions. These machine instructions are specified by opcode families derived from each of the basic function opcodes. For simplicity, we show only the opcode family for "add". Analogous families exist for each of the other basic functions.

add\_ror w,a,b,s // w = (a + b) rotate right s add\_rol w,a,b,s // w = (a + b) rotate left s add\_lsr w,a,b,s // w = (a + b) logical shift right s add\_lsl w,a,b,s // w = (a + b) logical shift left s add\_asr w,a,b,s // w = (a + b) arithmetic shift right s

Each of the arguments is an expression that specifies a value as follows:

w a register number or a special register wq or link.

a a register number or a special register pc, link, or rq.

**b** a register number or an absolute number 0..0x7f.

s an absolute number 0..31.

Note that the permissible range of absolute numbers in argument b is reduced considerably because of the necessity to specify a shift count.

The Beehive CPU version 2 omits *rotate left* since it is redundant with *rotate right*. Therefore Bas assembles *rotate left* s as *rotate right* 32 - s.

#### **3.10.4** Basic function with jumps

The Beehive CPU has machine instructions that conditionally jump to an address which is the result of any of the eight basic functions. These machine instructions are specified by opcode families derived from each of the basic function opcodes. For simplicity, we show only the opcode family for "add". Analogous families exist for each of the other basic functions.

```

call_add a,b // link = nextpc; goto (a + b)

a,b // goto (a + b)

j_add

a,b // if (ZERO) goto (a + b)

jz_add

a,b // if (MINUS) goto (a + b)

jm_add

jc_add

a,b // if (CARRY) goto (a + b)

jnz_add

a,b // if (!ZERO) goto (a + b)

jnm_add

a,b // if (!MINUS) goto (a + b)

jnc_add

a,b // if (!CARRY) goto (a + b)

a,b // class 1 jump 0

j0_add

j1_add

a,b // class 1 jump 1

a,b // class 1 jump 2

j2_add

j3_add

a,b // class 1 jump 3

j4_add

a,b // class 1 jump 4

a,b // class 1 jump 5

j5_add

j6_add

a,b // class 1 jump 6

j7_add

a,b // class 1 jump 7

```

Each of the arguments is an expression that specifies a value as follows:

a a register number or a special register pc, link, or rq.b a register number or an absolute number 0..0x1ffff.

#### 3.10.5 Class 1 jump instructions

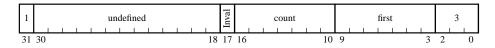

The Beehive CPU class 1 jump instructions are interpreted by special function units and generally they do not actually jump, although they fetch ALU operands in the normal way, which may include pulling a word from the read queue. To assist in specifying class 1 jump instructions that may have an unusual structure, Bas provides special opcodes. The following opcodes put "w" into the low-order four bits of the Rw field, and 0 into the Ra, Rb, Count, Const, and Fun fields:

```

j0w w // class 1 jump 0

j1w w // class 1 jump 1

j2w w // class 1 jump 2

j3w w // class 1 jump 3

j4w w // class 1 jump 4

j5w w // class 1 jump 5

j6w w // class 1 jump 6

j7w w // class 1 jump 7

```

Each of the arguments is an expression that specifies a value as follows:

w an absolute number 0..15.

The following opcodes put "x" into the Fun field and assemble "a" as ALU argument a and "b" as ALU argument b:

```

j0x x,a,b // class 1 jump 0

j1x x,a,b // class 1 jump 1

j2x x,a,b // class 1 jump 2

j3x x,a,b // class 1 jump 3

j4x x,a,b // class 1 jump 4

j5x x,a,b // class 1 jump 5

j6x x,a,b // class 1 jump 6

j7x x,a,b // class 1 jump 7

```

Each of the arguments is an expression that specifies a value as follows:

```

\mathbf{x} an absolute number 0..7.

```

a a register number or a special register pc, link, or rq.

**b** a register number or an absolute number 0..0x1fff.

#### 3.10.6 Synthesized loads

It may be observed that the Beehive CPU lacks instructions that load one register from another or from a constant. However, in many cases the desired effect can be obtained by employing a proper selection of ALU function and arguments. This is particularly effective if some register can be assumed to contain a useful value such as, for example, zero. See the .assume directive for how to tell the assembler about an assumed value. Bas provides the following synthesized load opcodes that assemble into a single machine instruction:

```

ld w,f // w = f

aqr_ld w,f // aqr = w = f (memory read)

aqw_ld w,f // aqw = w = f (memory write)

ror w,f,s // w = f rotate right s

rol w,f,s // w = f rotate left s

lsr w,f,s // w = f logical shift right s

lsl w,f,s // w = f logical shift left s

asr w,f,s // w = f arithmetic shift right s

```

Each of the arguments is an expression that specifies a value as follows:

w a register number or a special register wq or link.

**f** a register number; a special register **pc**, **link**, or **rq**; the absolute numbers 0 or 0xfffffff; or any constant offset up to plus or minus 0xfff (only 0x7f in the case of the shift opcodes) from an assumed register value.

```

s an absolute number 0..31.

```

Note that specifying a register number of \$29, \$30, or \$31 in argument f requires having an assumed zero register in order to get around Ra overloads. Note that special register **pc** always has an assumed value.

The Beehive CPU version 2 omits *rotate left* since it is redundant with *rotate right*. Therefore Bas assembles *rotate left* s as *rotate right* 32 - s.

#### **3.10.7** Synthesized jumps

As in the case of synthesized loads, Bas provides the following synthesized jump opcodes that assemble into a single machine instruction:

call f // link = nextpc; goto f

- j f // goto f

- jz f // if (ZERO) goto f

- jm f // if (MINUS) goto f

- jc f // if (CARRY) goto f

- jnz f // if (!ZERO) goto f

- jnm f // if (!MINUS) goto f

- jnc f // if (!CARRY) goto f

- j0 f // class 1 jump 0 alu=f

- j1 f // class 1 jump 1 alu=f

- j2 f // class 1 jump 2 alu=f

- j3 f // class 1 jump 3 alu=f

- j4 f // class 1 jump 4 alu=f

- j5 f // class 1 jump 5 alu=f

- j6 f // class 1 jump 6 alu=f

- j7 f // class 1 jump 7 alu=f

The argument f is an expression that specifies a value as follows:

**f** a register number; a special register **pc**, **link**, or **rq**; the absolute numbers 0 or 0xffffffff; or any constant offset up to plus or minus 0x1ffff from an assumed register value.

Note that specifying a register number of \$29, \$30, or \$31 in argument f requires having an assumed zero register in order to get around Ra overloads. Note that special register **pc** always has an assumed value. This is particularly useful in the case of synthesized jumps.

For the class 1 jumps, these instructions assemble to produce f as the output of the ALU, just like a normal jump would do. This may or may not be what you want.

#### 3.10.8 Load link immediate

The Beehive CPU has a "load link immediate" instruction that loads the **link** register with any constant whose low order four bits are zero:

lli i // link = i

x\_lli x // link = x

The argument is an expression that specifies a value as follows:

i an absolute number whose low order four bits are zero.x a relocatable offset. The loader will verify that the low order four bits are zero.

The x\_lli instruction can be used to get the address of a table into the **link** register provided that the table is properly aligned in memory, for example by using an .align 16 directive.

#### 3.10.9 Synthesized long loads

Any 32-bit value can be loaded into a register by using a "load link immediate" instruction to place the high order 28 bits in the **link** register followed by an "or" instruction to combine it with the low order 4 bits. Bas provides the following opcodes that assemble to this sequence:

long\_ld w,k // w = k

aqr\_long\_ld w,k // aqr = w = k (memory read)

aqw\_long\_ld w,k // aqw = w = k (memory write)

Each of the arguments is an expression that specifies a value as follows:

w a register number or a special register wq or link.k any absolute number or relocatable offset.

#### 3.10.10 Synthesized long jumps

Since the "load link immediate" instruction does not affect the condition codes, it can be used as a prefix to a conditional jump in order to jump conditionally to an arbitrary address. Bas provides the following synthesized long jumps that assemble into a sequence of two machine instructions:

```

long_call k // link = nextpc; goto k

long_j

k // goto k

long_jz

k // if (ZERO) goto k

long_jm

k // if (MINUS) goto k

k // if (CARRY) goto k

long_jc

long_jnz k // if (!ZERO) goto k

long_jnm k // if (!MINUS) goto k

long_jnc k // if (!CARRY) goto k

long_j0

k // class 1 jump 0 alu=k

long_j1

k // class 1 jump 1 alu=k

long_j2

k // class 1 jump 2 alu=k

long_j3

k // class 1 jump 3 alu=k

long_j4

k // class 1 jump 4 alu=k

k // class 1 jump 5 alu=k

long_j5

k // class 1 jump 6 alu=k

long_j6

k // class 1 jump 7 alu=k

long_j7

```

The argument k is an expression that specifies a value as follows:

k any absolute number or relocatable offset.

For the class 1 jumps, these instructions assemble to produce k as the output of the ALU, just like a normal jump would do. This may or may not be what you want.

#### 3.10.11 Simulator control

Bas provides the following instruction as a run-time interface to the simulator:

simctrl s // simulator control s

The argument s is an expression that specifies a value as follows:

s an absolute number 0..31.

This instruction assembles as Rw=0, Ra=0, Rb=0, const=0, count=s, Fun=OR, Op=NOSHIFT. Observe that in the Beehive CPU architecture this is equivalent to

or \$0,\$0,\$0

because the count field is irrelevant in such an instruction. However, the simulator notices this instruction and takes special actions based on s. See Section 5.5 for a discussion of the simulator controls.

## 3.11 Directives

A directive consists of an opcode possibly followed by some arguments. Although lexically an opcode is an identifier, it is not in the same namespace as predefined and user defined identifiers. In order to make clear which opcodes are instructions and which are directives, directive opcodes start with a period. The various directives are described next.

#### 3.11.1 Segment selection directives

Bas implements three kinds of segments: code, data, and absolute. Code segments are intended to contain code and data segments are intended to contain data. An absolute segment is intended to provide for the layout of data without defining its contents. Labels get the kind of the segment in which they are defined. There can be multiple code segments and multiple data segments. There is only one absolute segment. The code address rotation controls how the current location advances in code segments and in the absolute segment. Assembled instructions and data words can be emitted into code segments and data segments regardless of the kind of the segment. However, nothing can be emitted into the absolute segment.

The general directive for changing the current segment is:

```

.section n,s // switch to segment n characteristics s

.section n,s,b // switch to segment n characteristics s option b

```

The arguments are as follows:

- **n** an identifier that is the name of the new segment.

- s a string that defines characteristics of the new segment.

- **b** an identifier giving an additional option.

The string *s* is interpreted character-by-character and each character specifies a characteristic as follows:

a all labels in this segment should be retained for debugging.

- w segment is writable.

- x segment is executable.

- s segment is small.

- **S** segment contains strings.

- T segment is thread-local storage.

Characteristics other than "x" are ignored by Bas. Bas interprets characteristic "x" to specify a code segment. The absence of "x" specifies a data segment.

The optional argument b specifies options as follows:

@nobits the segment contains no initialized contents.@progbits the segment may contain content.

The @nobits option is used, for example, to specify a .bss segment. The option is ignored by Bas.

When changing the current segment, if the new named segment does not already exist it is created. Otherwise, Bas merely switches to the existing segment and extends it.

The following abbreviated directives can be used to change to the default code and data segments:

.code // switch to default code segment .text

.data // switch to default data segment .data

.bss // switch to secondary data segment .bss

Finally, the following directive changes to the absolute segment:

.abs i // switch to absolute segment location i

The argument i is an expression that specifies a value as follows:

i any absolute number.

The absolute segment does not have a name. Although words cannot be emitted into the absolute segment, its current location can be advanced. This makes it convenient to define absolute labels in laying out a structure.

#### 3.11.2 Advance current location directives

The following directive advances the current location within the current segment:

.blkw i // advance current location by i \* step .blkb i // advance current location by i bytes

The argument i is an expression that specifies a value as follows:

i any absolute number.

.blkw advances by a number of words and .blkb by a number of bytes.

The treatment of .blkb depends on the current segment's step. If the step is 4, implying a byte-addressed segment, .blkb advances the current location by i. If the step is 1, implying a word-addressed segment, .blkb advances the current location by (i + 3) / 4, which is the number of words it would take to store i bytes.

#### **3.11.3** Align current location directives

The following directives advance the current location within the current segment, if necessary, until it has a specified alignment:

.align i // advance current location until it is 0 mod i .alignw i // advance current location until it is 0 mod (i \* step)

The argument i is an expression that specifies a value as follows:

i any absolute number that is a power of two

Note that the current location need not be on a word boundary when current segment's step is 4. This can result from use of the .abs, .blkb, .byte, .string, or .ascii directives, for example. The .align directive is used to reestablish a desired alignment.

#### **3.11.4** Emit words or bytes directives

The following directives emit words or bytes into the current segment:

```

.word k,k,k,... // emit words

.long k,k,k,... // alias for .word

.byte k,k,k,... // emit bytes

.2byte k,k,k,... // emit bytes in chunks of 2

.3byte k,k,k,... // emit bytes in chunks of 3

.4byte k,k,k,... // emit bytes in chunks of 4

.short k,k,k,... // alias for .2byte

```

Each of the arguments k is an expression that specifies a value as follows:

**k** any absolute number or relocatable offset.

Multiple arguments separated by commas may be specified.

Emitting bytes gets very special treatment from the assembler. The ".byte" directive emits one byte for each argument, the ".2byte" directive emits two bytes for each argument, the ".3byte" directive emits three bytes for each argument, and the ".4byte" directive emits four bytes for each argument. The emitted bytes are taken from the argument value starting with its least significant byte. Argument values that require relocation *are permitted*. Any part of the argument value that is not emitted is just ignored.

If the current segment's step is 4, meaning that it is a byte-addressed segment, each byte is emitted at a consecutively higher byte address just as you might expect. However, if the current segment's step is 1, meaning that it is a word-addressed segment, the assembler groups the sequence of bytes into chunks of four, arranges each chunk into a word value, and emits the chunks into successive words.

Note that ".4byte" is not the same as ".word" because the former emits four bytes per argument regardless of where the word boundary falls, whereas the latter always checks for word alignment.

If you want to know why I had to implement all these crazy directives, gcc uses them when writing debugging information. Emitting byte values that require relocation can generate many relocation patches in the output file.

#### 3.11.5 Emit string directives

The following directives emit a string into the current segment:

```

.ascii z // emit string

```

```

.string z // emit string with null terminator

```

The argument z is a string of any length. The characters in the string are emitted in order effectively using .byte directives. In the case of .string an additional zero byte is emitted at the end.

#### **3.11.6 Region nesting directives**

Bas maintains a current region name as it processes the source input. Any identifier that starts with a "." (except for "." itself) is implicitly prefixed by the current region name. This permits labels and symbols to be abbreviated locally in a region. Regions can be nested.

```

.enter name // enter region

.leave name // leave region

```

The argument name is an identifier that is used to name the region. Note that if this identifier starts with "." it will itself be subject to the implicit prefix transformation. To make this work with nested regions, in both .enter and .leave the argument belongs to the enclosing region.

Opcodes are immune to the implicit prefix transformation.

#### 3.11.7 Assume register directives

The utility of the opcodes that synthesize instructions is greatly enhanced if some registers can be assumed to contain a known value, for example, zero. This is specified by the following directives:

```

.assume r,k // henceforth assume r = k

.noassume r // henceforth contents of r is unknown

```

Each of the arguments is an expression that specifies a value as follows:

```

r a register number.k any absolute number or relocatable offset.

```

The .assume applies to all subsequent source input lines until cancelled by a .noassume.

#### 3.11.8 Global symbol directive

A symbol is declared as global using the global symbol directive:

```

.globl n // declare symbol n as global

```

If the symbol is defined in the current assembly, then its name and definition is made available to the relocating loaded to bind external references. The definition must be an absolute number or a relocatable offset. If the symbol is not defined in the current assembly, then it signifies an external reference to a global symbol. The -x option causes all otherwise undefined symbols to be declared as global, unless they are specifically declared as local.

#### 3.11.9 Local symbol directive

A symbol is declared as local using the local symbol directive:

```

.local n // declare symbol n as local

```

The purpose of declaring a symbol as local is to override the presumption of the -x option with regard to a common request.

#### 3.11.10 Common request directive

A symbol is requested to be defined as the base address of a common area using the common request directive:

.comm n,s,a // request a common area

The common request directive requests that the symbol "n" be defined as the base address of a common area of size "s" bytes with alignment "a". The common area will be of kind "data" with the same address rotation as the data segment. The alignment "a" may be omitted, which case it defaults to the step of the data segment.

If the symbol "n" is declared as local, then this is a local common request, and it will be satisified by allocating space at the end of the data segment. The definition of "n" will be local and no other object file will be able to see it.

Otherwise, if the symbol "n" is declared as global, then this is a global common request. Global common requests of the same symbol made different object files are combined into a single request by taking the maximum of the requested sizes and the maximum of the alignment requirements.

#### 3.11.11 Include directive

A file can be incorporated into the source stream using the include directive:

```

.include z // include file "z" at this point

```

This file name z is a string. Each of the specified directories of include files is searched in order to find the indicated include file. The -I option is used to specify an include file directory.

#### 3.11.12 Commentary directives

The gcc compiler emits various directives related to debugging. For the present, the following directives are ignored:

.size n,k // declare size of symbol n to be k

.type n,... // declare type of symbol n

.file s // file name s

.ident s // compiler identification s

## **3.12** Predefined symbols

Bas manages a collection of predefined symbols. Some of these symbols have values that change as assembly progresses (which is not possible for user defined symbols). The predefined symbols are as follows:

**pc** the program counter special register, read via Ra overload 31 **link** the link special register, read via Ra overload 30 and written via Rw overload 30 **rq** the read queue special register, read via Ra overload 29 wq the write queue special register, written via Rw overload 31

. the current location in the current segment

code.rota the code segment address rotation (an absolute number)

data.rota the data segment address rotation (an absolute number)

**code.step** address offset between words in the code segment (an absolute number) **data.step** address offset between words in the data segment (an absolute number)

## Chapter 4

# Utilities

Various utility tools manipulate relocatable object files. The archiver collects relocatable object files into a library archive. The loader binds relocatable object files into an executable object file. The image maker converts an executable object file into a binary memory image. The Virtex mem file maker convers an executable object file into Virtex mem files. There is also a utility to process a file of bytes into C source that can then be compiled into a relocatable object file. These utilities are described next. The format of the object files is described in Appendix B.

## 4.1 Archiver - Bar

Bar combines a number of relocatable object files into a library archive. Bar is invoked using the command line

Bar command archive.a modulea.o moduleb.o ...

Bar adds the modules to the archive, creating the archive first if necessary. The command is a string of characters, each of which is interpreted separately. The following command characters are supported:

- **r** ("Replace") Add new modules to the end of the archive, deleting any existing ones with the same names.

- **q** (So-called "quick") Add new modules to the end of the archive, without deleting any existing ones that might have the same names.

- **c** ("Create") Expect to create the archive. The archive is always created if it does not already exist, but a warning is issued in such a case unless this command is specified.

- v ("Verbose") Give additional commentary on the actions taken.

Exactly one of "r" or "q" must be given. Any number of relocatable object files may be provided as input. You can also provide an archive as input, in which case all of the relocatable object files it contains are added to the archive being constructed.

The command line format conforms to that of the gnu archiver so that the gnu tool chains can use it.

## 4.2 Loader - Bld

Bld is a relocating loader. Bld reads a number of relocatable object files and archive files, resolves external symbol references, concatenates same-named segments, and outputs an executable object file. The format of the object file is described in Appendix B.

Bld is invoked using the command line

Bld [options] module.o library.a ...

Any number of relocatable object files and library archive files may be provided. The files are incorporated into the final executable in the order in which they appear on the command line. If the file is a relocatable object file, it is incorporated without further ado. If the file is a library archive file, its constituent object files are scanned to determine if any satisfies an external symbol reference and, if so, that object file is incorporated. If any object file is incorporated from a library archive, the archive is rescanned to see if additional object files need to be incorporated.

Options start with a hypen (-). The following options control relocation and are processed in the order they appear on the command line:

- -codebase=n Specify that code segments will be relocated to start at memory word index n (in hex). If there are multiple code segments, they are relocated in succession to start at the memory word index after the previously relocated code segment, in the order in which they are encountered as the input files are processed. Note that the memory word index is independent of the segment address rotation.

- -database=n Specify that data segments will be relocated to start at memory word index n (in hex). If there are multiple data segments, they are relocated in succession to start at the memory word index after the previously relocated data segment, in the order in which they are encountered as the input files are processed. Note that the memory word index is independent of the segment address rotation.

- -codefloat Specify that the code segments will be relocated to start at a memory word index after the previously specified kind of segment (if any).

- -datafloat Specify that the data segments will be relocated to start at a memory word index after the previously specified kind of segment (if any).

- The following options specify the name of various output files:

- -o a.out Specify that the output executable object file will be named a.out

- -map a.map Create a map file a.map listing the base word index and size of segments and the definitions of global symbols.

The following options control the loading of libraries. They can occur anywhere in the command line and are processed in order with other files that are loaded.

-Ldir Add dir to the library search path.

-**L***xxx* Find the library archive file *libxxx.a* on the library search path and load it as described above.

The following options control how *common* symbols are processed. A common symbol is created with a . comm assembler directive or with an uninitialized global non-extern variable declaration in C. Common symbols are weird in that multiple object files may declare them. The multiple declarations are combined by taking the largest length and most restrictive alignment requirement.

- -commbss Specify that common symbols should be allocated in the .bss segment. This is the default.

- -nocommbss Specify that common symbols should be allocated by creating a special data segment for each one. The segment is named by prefixing "comm-" to the name of the common symbol. This is the way the loader used to work.

The following options control how debugging segments are processed. When GCC is given the -g option it generates debugging information into data segments whose names start with ".debug\_". Such segments are called debugging segments.

- -debugseg Specify that debugging segments should be changed to have kind "debug", which causes them to be relocated separately from code and data segments and, more significantly, *not* to appear in the memory image created by Bimg or Bsim. This is the default.

- **-nodebugseg** Specify that debugging segments should be left as data segments. This is the way Bld used to work.

## 4.3 Image maker - Bimg

Bimg is the image maker. Bimg reads an executable object file, constructs a memory image by applying all specified patches, and outputs the result as a binary memory image file. The binary image file contains a consecutive range of memory words, starting with the word at the lowest memory word index loaded by the executable object file and continuing through the highest memory word index loaded by the executable object file.

Bimg is invoked using the command line

Bimg [options] a.out

One executable object file *a.out* is expected. Options start with a hypen (-). The following options are provided:

-img a.img Specify that the output binary memory image file will be named a.img instead of the default, which is to take the name of the input executable object file and replace the extension with .img

### 4.4 Virtex mem file maker - Bvmem

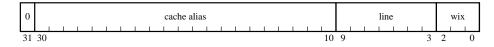

Bvmem makes Virtex mem files that can be used to initialize the cache memory of a Beehive design. Bvmem reads an executable object file, constructs separate code and data memory images by applying all specified patches, and outputs the results in Virtex mem file format. Each resulting Virtex mem file contains a consecutive range of memory words starting with word index zero and continuing through the last word loaded by the object file into that memory image. The format of these mem files is described in the Data2MEM Users Guide [2].

Note that the Beehive has separate code and data caches. Each cache is initialized to contents that appear to have been fetched from physical memory word indexes zero through 0x3ff. However, since the caches are separate, the initialized contents of the code and data caches are independent. The loader can relocate both the code segment and the data segment to start at word index zero, which is the proper arrangement for constructing Virtex mem files.

By mem creates two Virtex mem files, one for code and one for data. Given an input file *a.out* by default the resulting code Virtex mem file is named *acode.mem* and the resulting data Virtex mem file is named *adata.mem*. The extension .mem is required by the Virtex tools.

Bymem is invoked using the command line

```

Bvmem [options] a.out

```

One executable object file *a.out* is expected. Options start with a hypen (-). The following options are provided:

-mem b.mem Specify that the Virtex mem files will be named bcode.mem and bdata.mem instead of the default, which is to take the name of the input executable object file and replace the extension with code.mem and data.mem

## 4.5 File of bytes processor - Bfiledata

Bfiledata takes a file of bytes *file.dat* and produces a C source file *file.c* that defines and initializes two global symbols, *file* and *file\_cnt*. A header file *file.h* is also produced that contains external definitions for these symbols. The global symbol *file* is defined as an array of bytes and is initialized to the contents of the file of bytes. The global symbol *file\_cnt* is defined as an int and is initialized to the number of bytes in the array. Bfiledata is invoked using the command line

Bfiledata [options] file.dat

Options start with a hypen (-). The following options are provided:

- -c b.c Specify the name of the output C source file. The default is *file.c*

- -h b.h Specify the name of the output C header file. The default is file.h

- -gbl b Specify the name of the global that is initialized to the array of bytes. The default is *file*

-cnt *b\_cnt* Specify the name of the global that is initialized to the size of the array. The default is *file\_cnt*

## **Chapter 5**

# **Simulator - Bsim**

Bsim is a simulator for Beehive [1]. Bsim reads an object file, initializes a simulated memory image, and then simulates Beehive instructions beginning at the address of main. The format of the object file is described in Appendix B. The simulator implements the full physical memory space and a selectable number of normal cores, each with a full instruction set, instruction and data caches, debug unit, and most of the coprocessors.

## 5.1 Running Bsim

Bsim is invoked using the command line

Bsim [options] program.out

Options start with a hypen (-). The following options are supported:

- **-trace** Turn on instruction trace mode before starting the simulation. Instruction trace mode can also be turned on or off during simulation by using the simulator control instructions described in Section 3.10.11.

- -debug Activate the interactive debugger on core 1. The interactive debugger is described in Section 5.6.

- -ncore=n Set the number of normal cores to n. The default is 1 normal core. Note that all cores start execution at the same start address, either zero if there are any cache preload requests, or otherwise the global symbol main. Special startup code must be used to allocate a separate properly-aligned stack to each core.

- -megastepmax=n Set the maximum number of cycles that the simulator will execute to n million. Note that this number is in millions. It takes the simulator about a second per core to simulate a million cycles. The default is 0 which means no limit.

- -cachestat Print out cache statistics for each core and the end of simulation. This is the default.

-nocachestat Do not print out cache statistics for each core and the end of simulation.

-icache=n file.mem Add icache core n file.mem to the list of cache preload requests.

-icache file.mem Add icache core 0 file.mem to the list of cache preload requests.

-dcache=n file.mem Add dcache core n file.mem to the list of cache preload requests.

-dcache file.mem Add dcache core 0 file.mem to the list of cache preload requests.

## 5.2 Cache preload requests

The simulator supports preloading of instruction and data caches. This is requested by the -icache and -dcache options. There may be more than one request. The requests are processed in order, after the requested number of cores has been created and physical memory has been initialized.

Note that if there are any cache preload requests, the simulator will start execution of all cores at location zero. This corresponds to a reset in the hardware.

A cache preload request consists of (1) a specification of icache or dcache, (2) a core number, and (3) a file. If the core number is zero it is interpreted as applying to all cores, otherwise the preload request applies only to the indicated core, if present. The file is expected to be in vmem format such as created by Bvmem.

Preloading a cache initializes the contents of the cache as if the specified data had been fetched from addresses 0 through 0xfff. The cache lines are marked as valid and not dirty. The data is taken from the first 1024 words of the mem file. If the mem file contains fewer words, it is padded with zeros.

As an example, the following command preloads core 1 with "master" code and all other cores with "slave" code:

Bsim -icache slave.mem -icache=1 master.mem program.out

## 5.3 Physical memory

The simulator implements the full physical memory space of 0x80000000 words. However, actually trying to use the entire memory space will likely cause the simulator to exhaust its resources.

The simulator implements both the data cache and the instruction cache. Unless they have been preloaded, both caches are initially entirely invalid.

Data accesses are performed more rapidly than in the hardware, especially with regard to taking cache misses. The simulator is not cycle exact with respect to data accesses. An attempt to access a nonexistent memory address produces an error message.

The simulator supports all address rotation options. The code and data rotations are specified in the object file.

| supported | coprocessor                                        |

|-----------|----------------------------------------------------|

| yes       | 0: ASLI interface coprocessor (see Appendix A.6.2) |

| no        | 1: multiply coprocessor                            |

| no        | 2: miscellaneous output signal coprocessor         |

| yes       | 3: data cache controller (see Appendix A.6.3)      |

| yes       | 4: message controller (see Appendix A.6.4)         |

| yes       | 5: lock controller (see Appendix A.6.5)            |

|           |                                                    |

Table 5.1: Simulated coprocessors

### 5.4 Simulated coprocessors

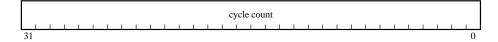

Table 5.1 summarizes the simulation support for the various Beehive coprocessors. At the start of simulation, the cycle counter is set to zero, all lines in the data cache are invalid, all receive message queues are empty, and no core holds any lock.

The simulator connects the ASLI interface register to the console. If the simulator is not run from a console (for example, when run from inside an emacs shell), then input is not possible due to deficiencies in Windows. In such a case output will happen normally but it will appear that the receiver never has a byte ready to read.

The simulator counts cycles starting with zero at the beginning of the simulation. A taken jump adds an extra cycle to account for the post jump nullify. Even though the simulated memory system is fast, there may also be stalls due to memory access.

## 5.5 Simulator controls

The simulator takes special notice of any instruction which has const=0 and Fun=OR. After interpreting such an instruction, it interprets the count field (which is unused in this instruction by the Beehive CPU architecture) as a special control. See the simctrl instruction in Section 3.10.11 for how to create such an instruction in the assembler. The controls are:

- **0** no operation

- 1 exit simulator (normal termination)

- 2 start tracing instructions onto the console output

- 3 stop tracing instructions

- 4 dump register file onto the console output

- **5** exit simulator (abnormal termination)

- 6-31 reserved

## 5.6 Interactive debugger

The simulator supports an interactive debugger attached to core 1. The debugger is activated using the -debug option. When active, the debugger breaks before the first simulated instruction and accepts commands from the console input. Simulation of all

| <cr></cr>            | (empty line) run until break       |

|----------------------|------------------------------------|

| i                    | implicit break on each instruction |

| S                    | implicit break on new subroutine   |

| g                    | run without implicit breaks        |

| dm <i>addr count</i> | dump count words of data memory    |

| cm addr count        | dump count words of code memory    |

| r                    | dump registers                     |

| trace y              | trace each instruction             |

| trace n              | do not trace each instruction      |

| q                    | quit                               |

| h                    | print help message                 |

|                      |                                    |

Table 5.2: Debugger commands

cores is frozen while the debugger is accepting commands. The debugger commands are summarized in Table 5.2. Each debugger command occupies an input line.

The debugger inspects each instruction (on core 1) before it is executed. The debugger can trace each instruction before execution or it can trace the instruction only when it breaks. Tracing means that the debugger prints out the current program counter and pending instruction in symbolic form. For example, the initial break typically produces a trace output such as

main+00000000: \$27 = \$27 ANDN \$27

This means that the current program counter is at offset 0 from global symbol "main" and the pending instruction is an ANDN that stores zero into register 27.

Note that the instruction printed in an instruction trace comes from the physical memory, as opposed to the code cache on core 1. This may be fixed in the future.

The debugger gets symbol definitions from the input files. Only global symbols are considered. Symbols are classified as code symbols or data symbols depending on which kind of segment they are defined in. The debugger assumes that a subroutine extends from one code symbol to the closest next one defined at a higher address.

The debugger can perform an implicit break on each instruction or on each change of subroutine. The execution of an exit-simulator instruction (see Section 5.5 also causes a break. Currently there is no provision for setting break points.

The debugger can dump words from code memory or from data memory. Note that these printouts come from physical memory rather than from the code and data caches of core 1. This may be fixed in the future. The address to dump must be specified in hexadecimal. This may also be fixed in the future. The address is interpreted according to the relevant address rotation.

## Appendix A

## **Beehive architecture**

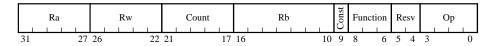

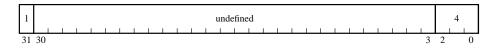

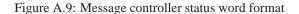

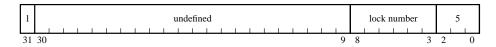

The Beehive architecture is based on a 32-bit word. It has a register file containing 32 registers, a two-input ALU followed by a full barrel shifter, and an unusual queued interface to a memory controller for access to data memory and memory mapped IO. Instruction space and data space may be considered as separate during execution of pre-initialized cache contents. (The Beehive hardware manual [1] should be consulted for further details.) In addition to the register file, there is a program counter register, a link register (for subroutine linkage and constant assembly), and a condition code register. All instructions have the same format, as shown in Figure A.1.

## A.1 ALU function

Almost all instructions select two arguments, A and B, for the ALU, which performs a function determined by the Function field:

0 A + B 1 A - B 2 A & B 3 A & ~B 4 A | B 5 A | ~B 6 A ^ B 7 A ^ ~B

#### A.1.1 ALU argument A

Argument A is specified by the Ra field. In most cases, Ra selects a register from the register file. However, certain values of Ra are overloaded. The Ra overloads are:

- 29 the read queue (takes one word; stalls until read queue is nonempty)

- **30** the link register

- 31 the program counter register (address of the current instruction)

Figure A.1: Beehive instruction format

#### A.1.2 ALU argument B

When Const = 0, argument B is specified by the Rb field, which selects a register from the register file. Rb > 31 is reserved.

When Const = 1, argument B is generated as a constant assembled from the instruction in a mode determined by the Op field. There are three modes: RbConst, CountRbConst, and RwCountRbConst.

**RbConst** the constant is the Rb field (7 bits).

**CountRbConst** the constant is the concatenation of the Count and Rb fields (12 bits). **RwCountRbConst** the constant is the concatenation of Rw[3:0], Count, and Rb fields

(16 bits). Note that in Beehive CPU version 2 the high order bit of the Rw field is not included in the constant.

In all cases the constant is padded on the left with 0s to fill out the 32-bit word.

### A.2 Major Operation

The Op field determines the constant mode, the shift mode, and various major effects of the instruction, as follows:

- 0 RbConst, logical shift right by Count bits, write result in Rw

- 1 RbConst, logical shift left by Count bits, write result in Rw

- 2 RbConst, rotate right by Count bits, write result in Rw

- **3** Load link immediate (see below)

- 4 RbConst, arithmetic shift right by Count bits, write result in Rw

- 5 CountRbConst, no shift, write result in Rw

- 6 CountRbConst, no shift, write result in Rw and into address queue as a write command

- 7 CountRbConst, no shift, write result in Rw and into address queue as a read command

- 8 RwCountRbConst, no shift, jump operation (see below)

- **9** RwCountRbConst, no shift, jump operation (see below)

- **10** RwCountRbConst, no shift, jump operation (see below)

- 11 RwCountRbConst, no shift, jump operation (see below)

- 12 RwCountRbConst, no shift, jump operation (see below)

- **13** RwCountRbConst, no shift, jump operation (see below)

- 14 RwCountRbConst, no shift, jump operation (see below)

- 15 RwCountRbConst, no shift, jump operation (see below)

| Rw[4] | Op | jump operation                   |

|-------|----|----------------------------------|

| 0     | 8  | call: link = nextpc, jump always |

| 0     | 9  | jump if minus                    |

| 0     | 10 | jump if zero                     |

| 0     | 11 | jump if carry                    |

| 0     | 12 | jump always                      |

| 0     | 13 | jump if not minus                |

| 0     | 14 | jump if not zero                 |

| 0     | 15 | jump if not carry                |